Research Area:

Responsible:

Participants:

Research Lines:

Project abstract

Reliability represents today the main constraint to the scaling of Flash non-volatile memories.

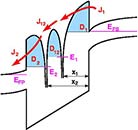

The research activity is focused on the analysis of the mechanisms limiting the reliability of ultra-scaled Flash memories and on the investigation of the operating conditions for the development of optimized technologies.

Anomalous charge loss from the floating-gate is characterized by novel experimental techniques and studied using advanced numerical models.

The project is based on a long term collaboration.

The research activity is now focused on the investigation of the threshold voltage instability due to single-electron trapping phenomena in the tunnel oxide of the memory cell and on its statistical characterization.

Project results

- R. Gusmeroli, C. Monzio Compagnoni, A. Riva, A.S. Spinelli, A.L. Lacaita, M. Bonanomi, and A. Visconti, “Defects spectroscopy in SiO2 by statistical random telegraph noise analysis”, in IEDM Tech. Dig., pp.483-486, 2006.

- D. Ielmini, A.S. Spinelli, and A. Visconti, “Characterization of oxide trap energy by analysis of the SILC roll-off regime in Flash memories”, IEEE Trans. Electron Devices, vol.53, pp. 126-134, 2006.

- D. Ielmini, A. Ghetti, A.S. Spinelli, and A. Visconti, “A study of hot-hole injection during programming drain disturb in Flash memories”, IEEE Trans. Electron Devices, vol.53, pp. 668-676, 2006.

- D. Ielmini, A. S. Spinelli and A. L. Lacaita, “Recent developments on Flash memory reliability”, Microelectron. Eng. 80C, 321-328, 2005.

- D. Ielmini, A. S. Spinelli, A. L. Lacaita, L. Chiavarone and A. Visconti, “A new charge-trapping technique to extract SILC-trap time constants in SiO2”, in IEDM Tech. Dig., IEEE Inc., Piscataway, NJ, 551-554 (2005). ISBN 0-7803-9268-X.

Patent:

A. Visconti, M. Bonanomi, D. Ielmini, A. S. Spinelli, “Method for programming/erasing a non volatile memory cell device, in particular for Flash type memories”. Domanda di brevetto congiunta STMicroelectronics-Politecnico di Milano depositata in data 10/3/06.