Research Area:

Responsible:

Participants:

Research Lines:

Project abstract

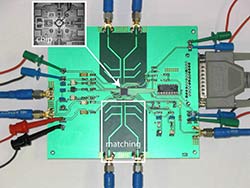

The project is a research collaboration between the DEI Politecnico and the Ericsson-Lab Italy. The subject of the investigation has been the design of a fully-integrated Phase Locked Loop (PLL) frequency synthesizer, for RF applications.

The generated signal of interest is a 64 QAM in the 4.4 – 5.5 GHz bandwidth. This kind of modulation implies very tight phase noise requirements, about -100 dBc/Hz @100 kHz offset, a quite challenging specification for the 0.5 um SiGe BiCMOS technology adopted. A fractional-N PLL architecture has been selected, while a new voltage controlled oscillator (VCO) implemented as 4 in-phase coupled single oscillators has been designed in order to achieve the low phase noise requirements. PLL successfully completed.

Project results

The project has been carried out in two steps. First, only the coupled oscillator, the most critical element, has been designed and tested. Then the entire PLL has been integrated. Some preliminary results have been published and patented:

- Proc. IEEE Custom Integrated Circuits Conference, pp. 269-272, Oct. 2004, Orlando Florida.

- Proc. of 11-th IEEE International Conference on Electronics, Circuits and Systems, pp. 29-32, Tel Aviv (Israel), Dec. 2004.

- C. Samori, L. Romanò, “Oscillatore LC” Domanda di brevetto N. MI2004A000156 – 2 Febbraio 2004.