Area di ricerca:

Responsabile:

Partecipanti:

Linee di ricerca:

Sommario

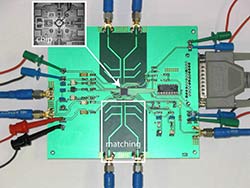

Il progetto è stato svolto in collaborazione con Ericsson-Lab Italy, e ha riguardato la realizzazione di un sintetizzatore di frequenza, implementato con struttura di anello ad aggancio di fase (PLL), completamente integrato per applicazioni alle comunicazioni a radiofrequenza.

La banda di interesse è quella tra 4.4 e 5.5 GHz, la modulazione è una 64 QAM, che comporta delle specifiche di rumore di fase piuttosto stringenti per un oscillatore integrato, dell’ordine di –100 dBc/Hz @ 100 kHz. La tecnologia per l’integrazione è la BiCMOS in SiGe di IBM.

Le caratteristiche di risoluzione di frequenza e di rumore hanno condotto alla scelta di una architettura di PLL a divisore frazionario, l’oscillatore controllato in tensione è realizzato con una nuova struttura comprendente 4 oscillatori accoppiati in fase. Il test dell’intero PLL è concluso.

Risultati del progetto ed eventuali pubblicazioni scientifiche/brevetti

Il progetto ha comportato prima l’integrazione del solo oscillatore, l’elemento più critico del sistema, quindi dell’intero PLL.

Alcuni risultati sono stati pubblicati e sono stati oggetto di un brevetto:

- Proc. IEEE Custom Integrated Circuits Conference, pp. 269-272, Oct. 2004, Orlando Florida.

- Proc. of 11-th IEEE International Conference on Electronics, Circuits and Systems, pp. 29-32, Tel Aviv (Israel), Dec. 2004.

- C. Samori, L. Romanò, “Oscillatore LC” Domanda di brevetto N. MI2004A000156 – 2 Febbraio 2004.